《ASTRA-SIM: Enabling SW/HW co-design exploration for distributed DL training platforms》

1. 文章简介

1.1 摘要

现代深度学习系统主要依靠基于高性能加速器(如 TPU、GPU)的硬件平台进行分布式训练。目前的例子包括谷歌的云 TPU 和 Facebook 的 Zion。DNN 训练涉及 DNN 模型架构、并行化策略、调度策略、集体通信算法、网络拓扑和终端加速器之间复杂的相互作用。随着人工智能/ML 模型的创新不断加速发展,需要一种全面的方法来理解和驾驭未来系统中复杂的 SW/HW 设计空间,以支持未来 DNN 模型的高效训练。在这项工作中,我们做出了以下贡献:(i) 为分层扩展结构上的分布式训练建立了 SW/HW 设计空间;(ii) 开发了一个用于导航设计空间的网络模拟器;(iii) 展示了算法拓扑协同设计加速端到端训练的前景。

1.2 研究动机

对模型架构、并行策略、调度算法、集合通信、网络拓扑、终端算力的仿真

大规模并行训练成本高,在实际部署和训练之前,需要一个仿真工具进行评估

1.3 主要贡献

为分层加速器结构设计空间探索建立 SW/HW 设计空间,并确定扩展 DL 工作负载的关键瓶颈

开发名为 ASTRASIM 的端到端网络模拟器,用于评估设计空间的各个方面

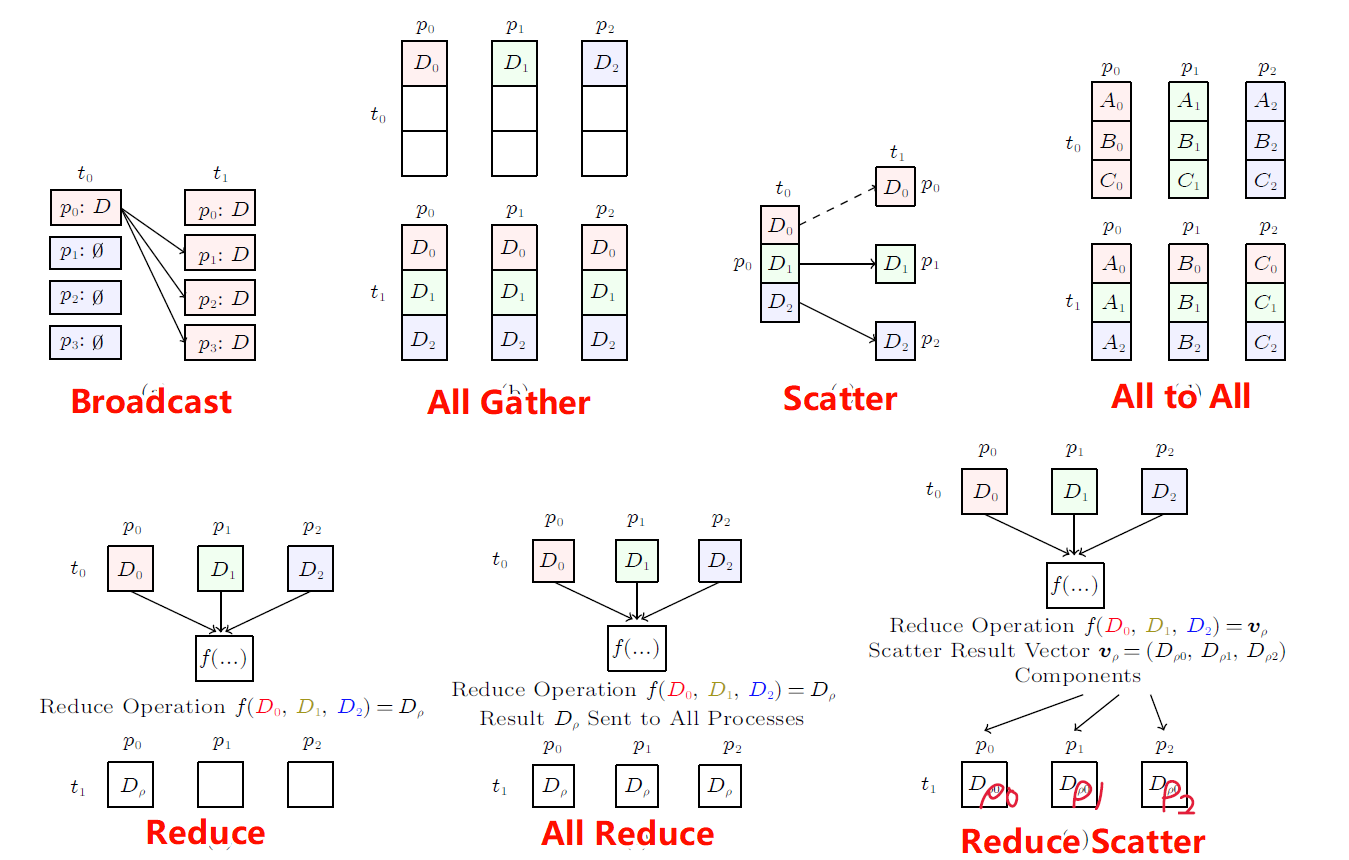

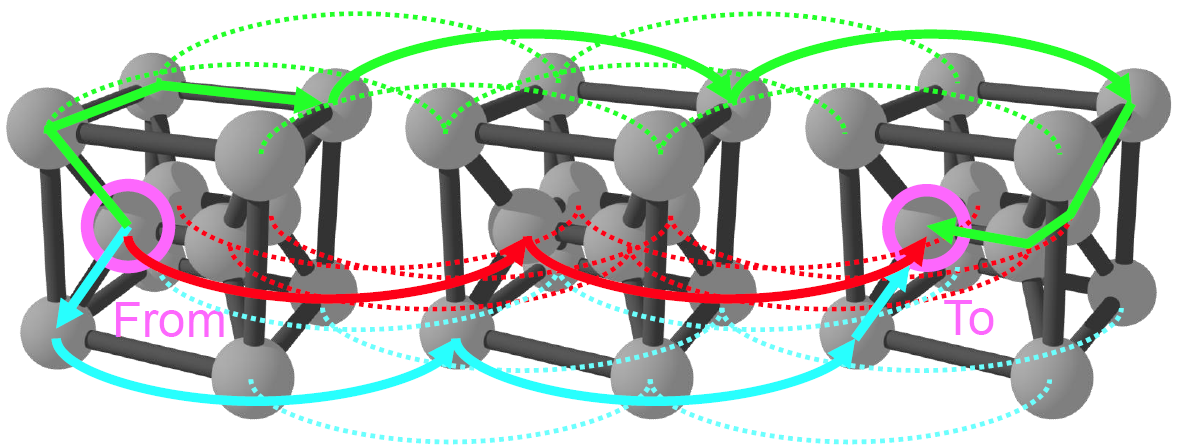

使用 ASTRA-SIM 对 alltoall 和 Torus 拓扑的 all-reduce 和 all-to-all 集合的一维、二维和三维拓扑进行全面分析

2. 实现方法

3. 实验结果

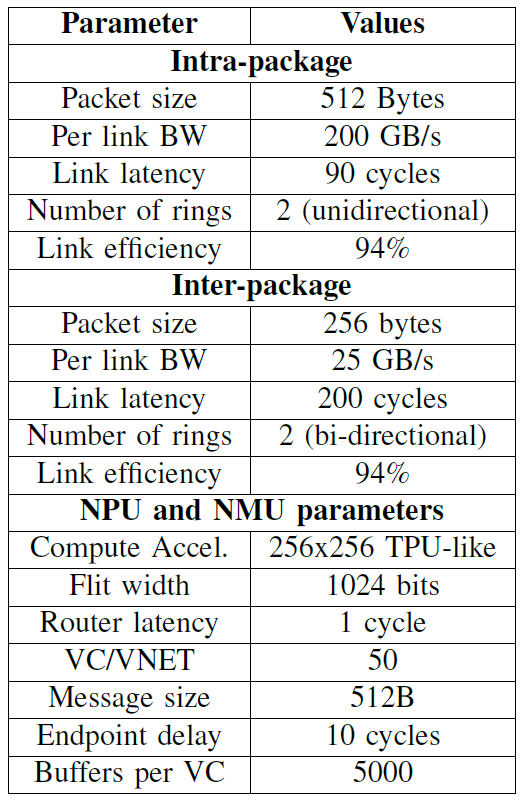

实验参数

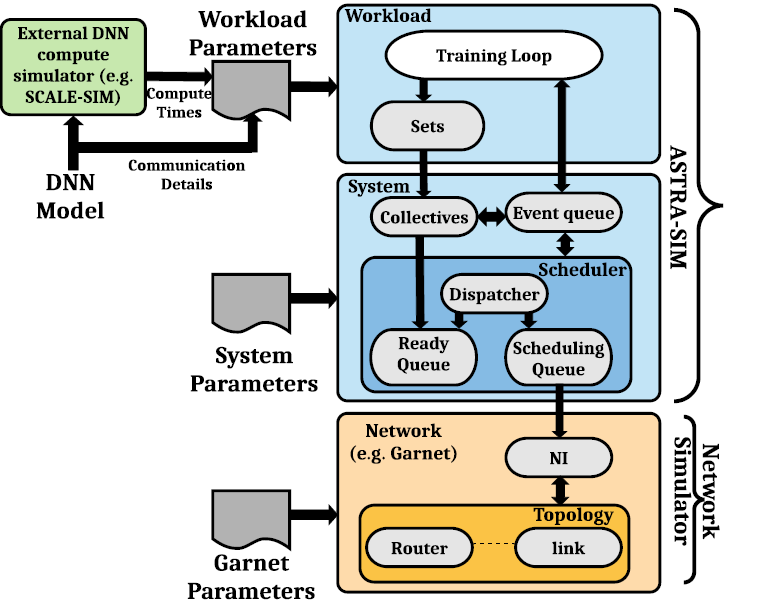

这项工作介绍了一种名为 ASTRA-SIM 的模拟器,用于阐述和浏览分布式 DL 训练平台的硬件/软件设计空间。我们重点关注分级放大结构上集体通信算法的详细建模,并实现端到端网络仿真。

《ASTRA-sim2.0: Modeling Hierarchical Networks and Disaggregated Systems for Large-model Training at Scale》

1. 文章简介

1.1 摘要

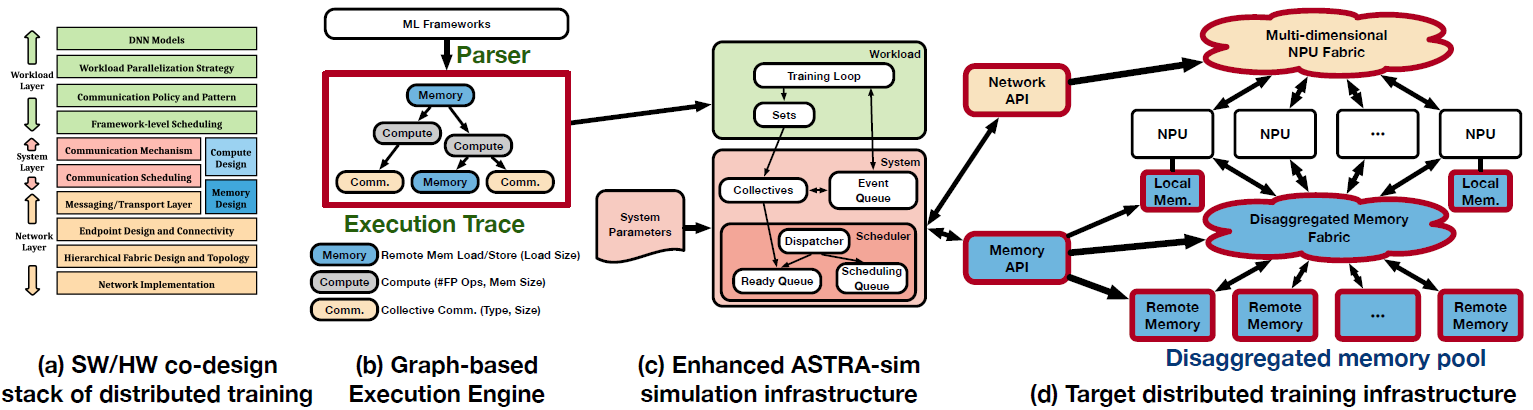

由于深度学习模型和输入数据正以前所未有的速度扩展,因此不可避免地要转向分布式训练平台,以适应模型并提高训练吞吐量。最先进的方法和技术,如晶圆级节点、多维网络拓扑结构、分解存储器系统和并行化策略,已被新兴的分布式训练系统积极采用。这导致分布式训练的 SW/HW 协同设计堆栈非常复杂,因此需要建模/仿真基础设施来探索设计空间。在本文中,我们扩展了开源的 ASTRA-sim 基础设施,并赋予其对最先进的和新兴的分布式培训模型和平台进行建模的能力。更具体地说,(i) 我们通过基于图的训练环路实现,使 ASTRA-sim 能够支持任意模型并行化策略;(ii) 我们实现了可参数化的多维异构拓扑生成基础架构,该基础架构具有分析性能估算,能够大规模模拟目标系统;(iii) 我们增强了内存系统建模,以支持网络内集体通信和分解内存系统的精确建模。利用这些功能,我们针对新兴的分布式模型和平台进行了全面的案例研究。这种基础架构可让系统设计人员迅速穿越复杂的协同设计堆栈,并在设计和部署大规模分布式训练平台时提供有意义的见解。

1.2 研究动机

ASTRA-sim v1.0对限制了它对任意并行策略、网络和内存模型的支持,它在设计和实现的时候并没有针对现有的DP、MP等策略

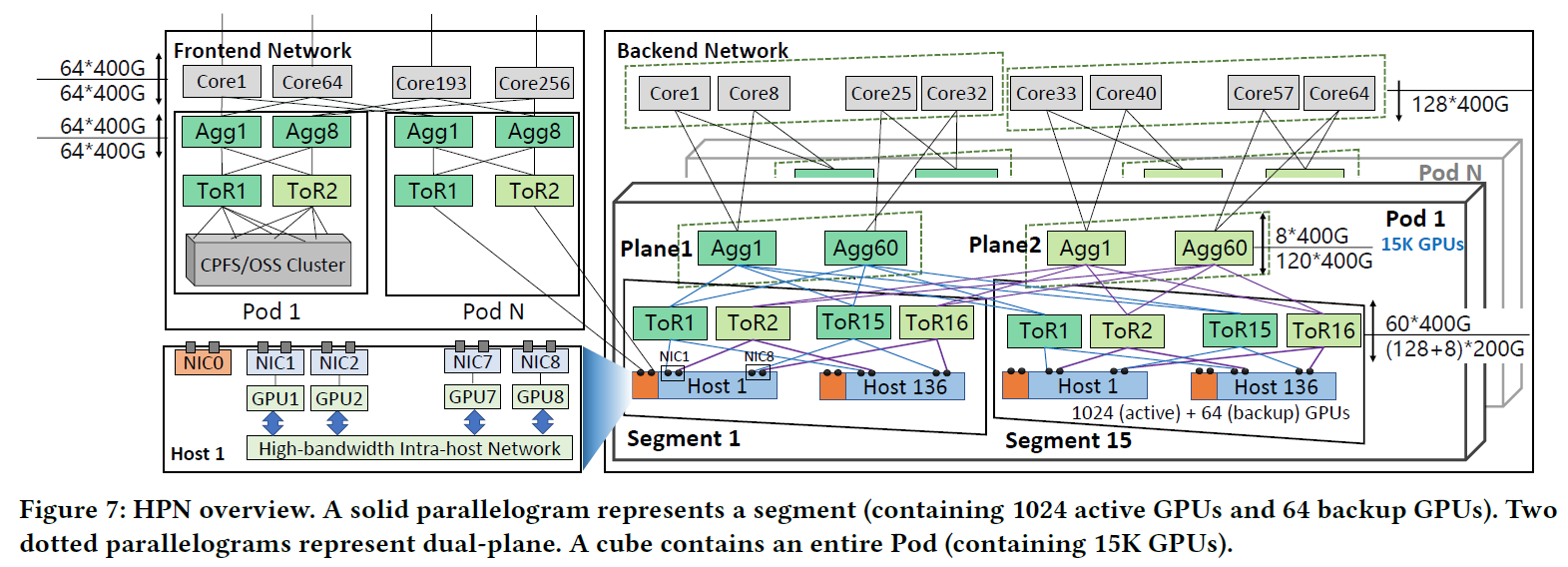

目前现有的网络大多是分层的复杂网络拓扑结构

ASTRA-sim v1.0不支持对分布式内存仿真的内容

1.3 主要贡献

开源的ASTRA-sim仿真软件

可以支持任意模型的并行策略,ASTRA-sim是基于图实现的

可参数化的基础架构

构建内存模拟系统

ASTRA-sim支持任意并行策略

ASTRA-sim支持分层的网络架构

ASTRA-sim支持内存建模

2. 实现方法

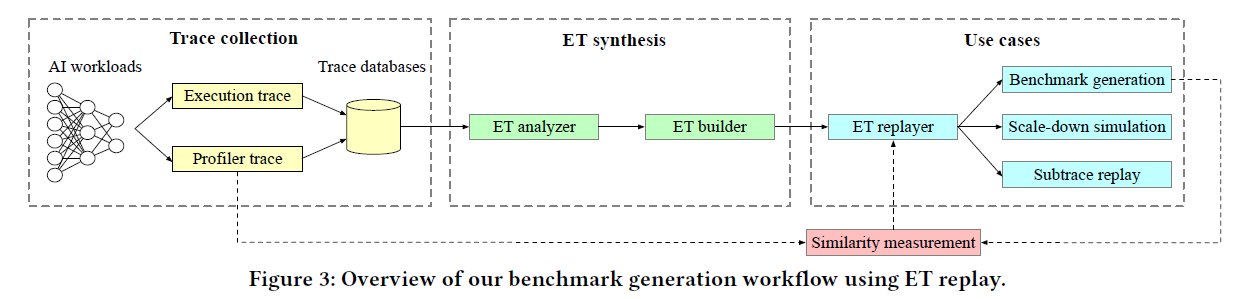

基于图的执行引擎,支持Pytorch、Tensorflow、FlexFlow等框架

多维度网络拓扑构建,支持分层网络构建

Analytical的网络后端

添加内存模型可以支持本地内存、远程内存、交换机内部集合通信的建模

3. 实验结果

调度的影响、Wafer规模的影响

分布式内存的影响